2025年7月22日,在第八屆智能輔助駕駛大會上,地平線芯片產品總監沈建指出,隨著電子電氣架構向中央集成與計算階段演進,輔助駕駛算法與芯片面臨更高要求,尤其是端到端與大模型技術的應用,使得芯片需具備高算力、高帶寬和低延遲特性。他介紹到,地平線通過提升單芯片算力、優化系統效率及降低功耗等措施,積極應對這些挑戰。

沈建還表示,地平線在芯片架構上不斷創新,歷經三代演進至Nash架構,實現了CNN和Transformer處理性能的顯著提升,并解決了Memory Wall問題。此外,地平線的征程6系列芯片全階覆蓋高、中、低三檔市場,其中J6P芯片算力高達560 TOPS,將于年內量產。

沈建|地平線芯片產品總監

以下為演講內容整理:

地平線是全場景輔助駕駛領域的全球領導者。公司以技術為導向,現有研發人員超2000人,專利數量也有2000余項。公司在國際挑戰賽及頂級學術會議上屢獲佳績,相關成果在輔助駕駛領域廣受行業認可。商業化方面,截至今年第一季度,征程系列出貨量已突破800萬套,成績斐然。

市場占有率方面,2023年,公司在自主品牌輔助駕駛解決方案市場中市占率位居行業第二。至2024年,公司市占率進一步提升,超過33%,每三臺配備輔助駕駛系統的車輛中,就有一臺采用地平線的解決方案。

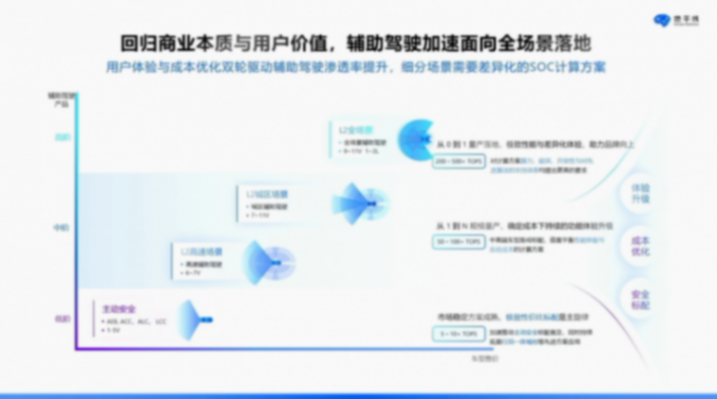

關于當前的行業發展趨勢,從產品維度來看,目前市場可劃分為高、中、低三檔。低階即入門級產品,該領域已基本成為紅海市場,其核心訴求在于安全與性價比。中階產品方面,隨著去年及今年輔助駕駛普及進程的加速,預計在2025年至2026年,中階產品出貨量將發生質變,滲透率也將迅速提升。高階產品領域,國內企業與特斯拉在高階輔助駕駛的探索上從未停歇。

得益于各大廠商在端到端與大模型技術方面的努力,行業在各類場景及corner case上取得了顯著進步,用戶體驗也大幅提升。然而,與人類駕駛水平或理想體驗相比,仍存在一定差距,需持續努力與探索。

圖源:演講嘉賓素材

從多個維度分析,我們認為有三點至關重要。一是安全,無論高中低檔產品,均需將安全置于首位。二是輔助駕駛的滲透率,當前及未來兩三年內,其滲透率預計將維持高位,這意味著對域控制器及一體機的成本要求將日益提升。三是隨著滲透率的提高,輔助駕駛的使用人群將不斷擴大,進而對用戶體驗提出更高要求。若用戶體驗持續優化,則輔助駕駛的普及程度將進一步提升,這也是全行業共同追求的目標。

系統層面,電子電氣架構歷經多年演進,已從分布式架構發展至區域控制,進而邁向中央集成與中央計算階段。電子電氣架構的變革有效降低了整車的成本。此外,為提升輔助駕駛體驗,各類異構計算單元的ECU正逐步向中央計算的SoC方向演進。這一演進對于降低成本及提升輔助駕駛體驗具有實際意義。

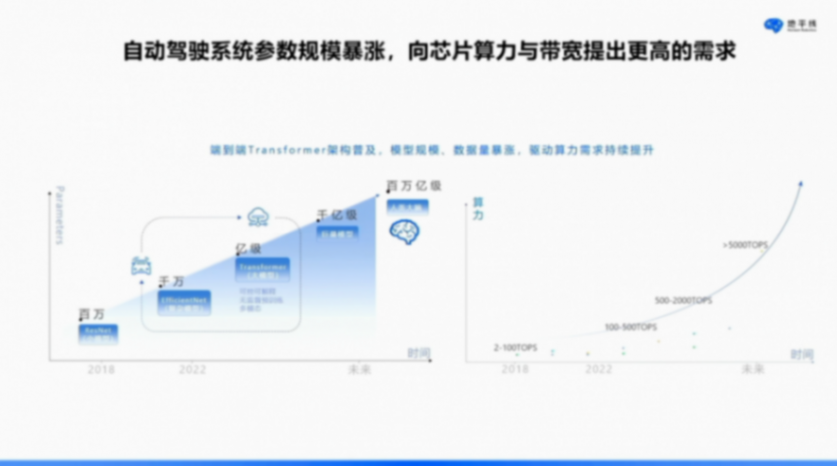

回歸輔助駕駛算法與芯片本身,在 2024、2025 年相關討論中,“端到端”與“大模型”是兩個高頻詞匯,其中涉及 VLM、VLA 等技術。這些技術在提升輔助駕駛體驗方面發揮了顯著作用,但其代價亦不容忽視。這些模型的參數規模極為龐大,基本達到零點幾億級別,領先的技術模型參數規模更已達到數億級別。如此龐大的模型參數對芯片性能提出了更高要求。此外,當前多數系統的幀率仍處于10~20幀水平,但預計在未來將逐步提升至更高幀率。因此,從算力層面來看,芯片需滿足日益增長的性能需求。

值得注意的是,無論是端到端技術還是大模型,其底層架構均基于Transformer。Transformer作為一種帶寬敏感型網絡,隨著參數量和幀率的增加,對芯片帶寬的要求也顯著提升。我們認為下一代芯片需具備高算力、高帶寬和低延遲三大核心特性。

圖源:演講嘉賓素材

針對以上問題,我們認為首先需實現單芯片算力的有效突破。提升單芯片算力最直觀的思路是先提升單代芯片性能,之后通過Chiplet技術等橫向擴展手段,進一步增強整體性能。當前,提升單代算力較為直接的方式是采用先進制程工藝。目前,這一方向仍將持續推進,例如從現有的7nm制程向5nm、4nm乃至3nm制程演進。然而,制程升級帶來的性能提升紅利正在逐步減弱,因此需要依靠系統協同來實現算力的有效突破。

此外,算力提升并非僅依賴于增加加速器的計算能力,更重要的是確保數據能夠及時、高效地傳輸至加速器,從而提升整體系統效率,實現較高的幀率表現。這是單代芯片性能提升的關鍵所在。

算力的提升并非無限制的,其最終需滿足車載部署的實際需求。鑒于當前車載散熱系統中冷卻液溫度大多維持在65度左右,這對芯片能效提出了極高要求。在輔助駕駛芯片中,NPU的功耗最高,因此設計高效能的NPU成為關鍵。此外,通過采用近存計算技術及優化后端物理實現,亦可進一步降低功耗,從而實現算力的有效提升。

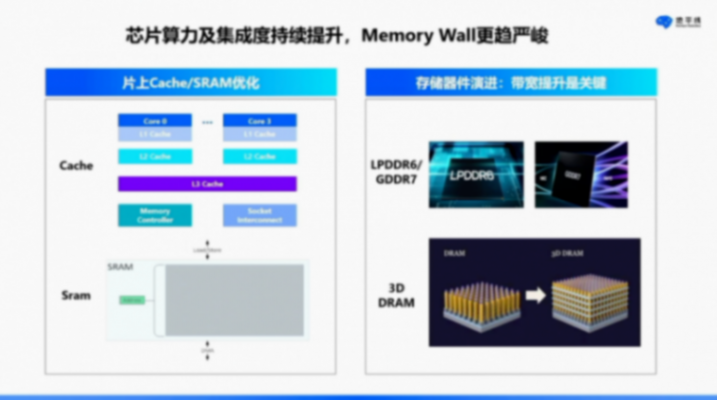

此外,還存在Memory Wall問題。隨著算力提升以及集成度增高,這一問題將愈發嚴峻。針對此問題,我們的思考主要圍繞兩個維度展開。

一是關注片內的SRAM和Cache。算力提升需以數據有效傳輸為支撐,而片內的CPU Cache以及NPU SRAM等模塊雖具備極高的數據傳輸速率,但容量相對有限。為解決這一問題,需依賴外部存儲器如DDR,其特點在于容量較大,可滿足當前大模型的存儲需求。然而,DDR的速率與片上SRAM存在較大差距,因此提升外部存儲帶寬成為關鍵任務。

圖源:演講嘉賓素材

二是架構層面。當前市場上較為常見的架構是DSA,例如地平線的BPU以及的昇騰系列均屬于此類架構。DSA架構的特點在于能效表現優異,但其設計主要面向特定領域,因此在通用性方面相較于通用GPU存在一定差距。為應對場景的多樣性需求,當前DSA架構也在逐步融入通用性加速單元。例如,GPU廠商在面向深度學習領域時,開發了GPGPU結合Tensor Core的方案,該方案在通用性方面表現良好,但在能效和性能上仍不及DSA架構。

而,鑒于行業共同目標均是推進更高級別的輔助駕駛技術發展,為適應未來場景的多樣性以及算法的通用性需求,通用計算架構與專用計算架構的融合將成為趨勢。地平線現有的BPU基于DSA架構,但未來將向融合通用計算能力的方向演進。

后摩爾時代,單純依靠工藝提升芯片性能的難度正日益增大。以業界情況來看,在更先進的A14、A16等制程上,廠商已轉向通過DTCO方向來挖掘性能潛力。對于輔助駕駛芯片而言,同樣需要采取類似策略,通過芯片底層定制標準單元、實現高性能物理設計,以及優化芯片架構中計算單元與總線的協同,從而將芯片性能發揮到極致。系統層面亦可借鑒此思路,集成更多加速模塊。同時,在算法層面,推動算子與芯片的協同設計,開展更多定制化代碼設計,以進一步提升性能。通過上述多維度的協同優化,不僅能夠提升性能,還能在一定程度上降低能耗,進而減少散熱與供電成本,實現系統整體優化。

在過去十年間,地平線在這一領域進行了諸多實踐。2016年,地平線提出了“智能計算時代的新摩爾定律”。彼時,業界普遍認為芯片片上算力即代表實際算力,但時至今日,客戶在評估芯片性能時,更傾向于通過實際測試板卡來驗證,這反映出芯片實際性能的發揮不僅取決于芯片本身的計算能力,還涉及編譯器優化、算法優化等多個層面。因此,唯有實現軟硬件協同優化,才能充分釋放芯片性能。

自2016年起,地平線的芯片架構歷經三代演進,從初代的Bernoulli架構,到后續的Bayes架構,再到2021年推出的Nash架構。目前,地平線量產的征程6系列芯片即基于Nash架構打造。

關于Nash架構的特性,回顧BPU六年來的發展歷程,其在CNN處理性能上實現了246倍的提升,在Transformer處理性能上則提升了27倍。此外,該架構新增了VPU,旨在增強芯片的通用性。同時,針對Transformer中常用的特定超越函數,我們采用了硬件固化設計,以此進一步提升Transformer的整體性能。在存儲系統方面,Nash架構引入了全新的三級存儲層次結構,通過協同總線與外部DDR存儲器的優化配合,有效解決了Memory Wall問題。

圖源:演講嘉賓素材

隨著J6B芯片近期完成回片測試,我們的征程6系列已實現全階通關成熟,全面覆蓋高、中、低三檔市場。其中,中階的征程6E與征程6M兩款芯片已于去年年底實現量產,高階和低階的產品也將很快量產。征程6B也已牽手,將于2026年年中量產。

在高階產品領域,地平線將持續突破創新,致力于為客戶提供極致體驗。而征程J6B芯片則聚焦于夯實基礎性能,將安全性能作為核心標配,嚴格遵循安全第一的重要準則。

此外,征程J6P芯片的算力高達560 TOPS,配備18個A7八核處理器,內部CNN總線帶寬達到1Tb/s,圖像處理帶寬性能達5.3Gpixel/s,同時內置MCU以幫助客戶降低成本,其帶寬超過200G。搭載征程6P的HSD城區輔助駕駛方案,將于Q3在奇瑞星紀元E05首發量產。